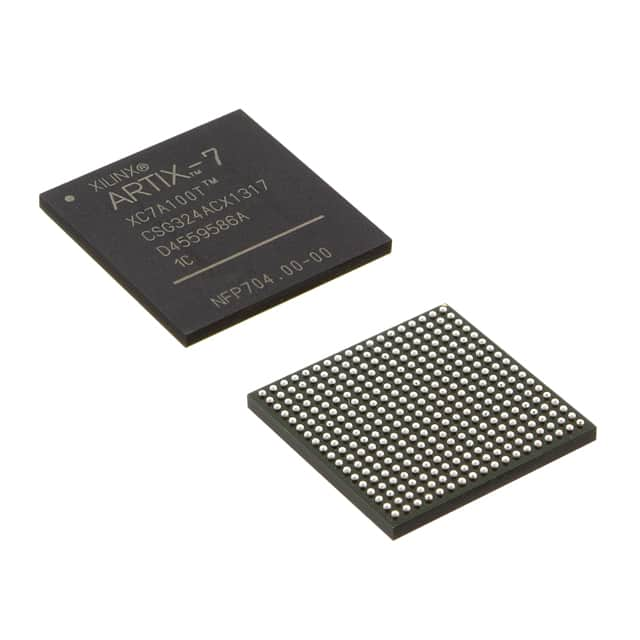

Xip IC original programable XCVU440-2FLGA2892I IC FPGA 1456 I/O 2892FCBGA

Atributs del producte

| TIPUS | DESCRIPCIÓ |

| Categoria | Circuits integrats (CI) |

| Mfr | AMD Xilinx |

| Sèrie | Virtex® UltraScale™ |

|

| Caixa |

| Estàndardd Paquet | 1 |

| Estat del producte | Actiu |

| Nombre de LAB/CLB | 316620 |

| Nombre d'elements lògics/cel·les | 5540850 |

| Bits de RAM totals | 90726400 |

| Nombre d'E/S | 1456 |

| Tensió - Alimentació | 0,922 V ~ 0,979 V |

| Tipus de muntatge | Muntatge en superfície |

| Temperatura de funcionament | -40 °C ~ 100 °C (TJ) |

| Paquet / Estoig | 2892-BBGA, FCBGA |

| Paquet de dispositius del proveïdor | 2892-FCBGA (55×55) |

| Número de producte base | XCVU440 |

Ús d'FPGA com a processadors de trànsit per a la seguretat de la xarxa

El trànsit cap a i des dels dispositius de seguretat (tallafocs) s'encripta a diversos nivells, i el xifratge/desxifrat L2 (MACSec) es processa als nodes de xarxa de la capa d'enllaç (L2) (interruptors i encaminadors).El processament més enllà de la L2 (capa MAC) inclou normalment un anàlisi més profund, desxifrat de túnels L3 (IPSec) i trànsit SSL xifrat amb trànsit TCP/UDP.El processament de paquets implica l'anàlisi i la classificació dels paquets entrants i el processament de grans volums de trànsit (1-20 M) amb un alt rendiment (25-400 Gb/s).

A causa del gran nombre de recursos informàtics (nuclis) necessaris, les NPU es poden utilitzar per a processament de paquets a una velocitat relativament més alta, però no és possible un processament de trànsit escalable d'alt rendiment i de baixa latència perquè el trànsit es processa mitjançant nuclis MIPS/RISC i programant aquests nuclis. en funció de la seva disponibilitat és difícil.L'ús d'aparells de seguretat basats en FPGA pot eliminar eficaçment aquestes limitacions de les arquitectures basades en CPU i NPU.

Processament de seguretat a nivell d'aplicació en FPGA

Els FPGA són ideals per al processament de seguretat en línia en tallafocs de nova generació perquè compleixen amb èxit la necessitat d'un major rendiment, flexibilitat i operació de baixa latència.A més, els FPGA també poden implementar funcions de seguretat a nivell d'aplicació, que poden estalviar encara més recursos informàtics i millorar el rendiment.

Alguns exemples comuns de processament de seguretat d'aplicacions en FPGA inclouen

- Motor de descàrrega TTCP

- Concordança d'expressions regulars

- Processament de xifratge asimètric (PKI).

- Processament TLS

Tecnologies de seguretat de nova generació amb FPGA

Nombrosos algorismes asimètrics existents són vulnerables al compromís dels ordinadors quàntics.Els algorismes de seguretat asimètrics com RSA-2K, RSA-4K, ECC-256, DH i ECCDH són els més afectats per les tècniques de computació quàntica.S'estan explorant noves implementacions d'algorismes asimètrics i estandardització NIST.

Les propostes actuals per al xifratge postquàntic inclouen el mètode d'aprenentatge d'anells per error (R-LWE) per

- Criptografia de clau pública (PKC)

- Signatures digitals

- Creació de claus

La implementació proposada de la criptografia de clau pública inclou determinades operacions matemàtiques conegudes (TRNG, mostreig de soroll gaussià, addició de polinomis, divisió de quantificadors de polinomis binaris, multiplicació, etc.).La IP FPGA per a molts d'aquests algorismes està disponible o es pot implementar de manera eficient mitjançant blocs de construcció FPGA, com ara motors DSP i AI (AIE) en dispositius Xilinx existents i de propera generació.

Aquest document blanc descriu la implementació de la seguretat L2-L7 mitjançant una arquitectura programable que es pot desplegar per a l'acceleració de seguretat en xarxes perifèriques/d'accés i tallafocs de nova generació (NGFW) a les xarxes empresarials.